Download Original Japanese press-release as PDF

Edgecortix Inc. (Headquarters: Tokyo, Japan, CEO: Sakyasingha Dasgupta, hereafter called “EdgeCortix”) has signed a partnership with PALTEK Corporation (Headquarters: Yokohama, Japan, President: Naohide Yabuki, Securities Code: 7587, hereinafter called “PALTEK”), which sells and designs semiconductors and related products. Since its founding in 1982, PALTEK has used FPGAs to provide product development support and technical support to Japanese electronics manufacturers. The company’s strength, cultivated through its semiconductor sales, lies in its ability to support customers from proposal through to mass production, and along with integrated design services.

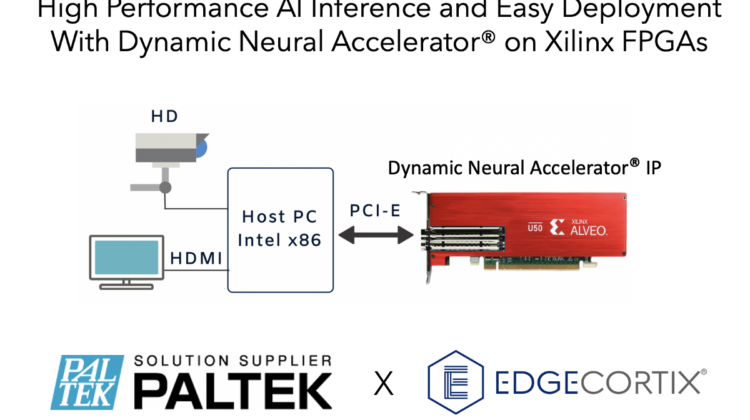

Through this partnership, EdgeCortix will provide PALTEK, with their low-latency, energy-efficient hardware IP (intellectual property) Dynamic Neural Accelerator® and MERA ™ compilers, to be implemented on the Xilinx Accelerator Card “Alveo ™ U50 Data Center Accelerator Card” *1. This enables high-throughput, real-time and low power edge AI applications in areas such as ADAS (advanced driver assistance systems), autonomous driving, robots, smart cities, drones, industry 4.0, etc.

Background and outline of this collaboration

In recent years, deep learning, which is part of a broader family of machine learning methods based on artificial neural networks, has realized dramatic improvements in accuracy in many fields such as machine vision and voice processing. However, majority of the current practical applications are based on cloud-infrastructure using GPUs. In general for edge computing, there are many use cases that cannot be processed efficiently in the cloud due to challenges arising from communication volume, load, and latency during inference, with the performance of inference processing on edge devices using streaming data becoming a critical issue.

EdgeCortix is a fabless semiconductor design company, co-designing the hardware and software for low latency artificial intelligence inference processors on embedded and telco edge devices. Through this distributor agreement, EdgeCortix’s unique AI hardware IP, the Dynamic Neural Accelerator® *2, can be implemented on the Xilinx Alveo™ U50 FPGA accelerator cards provided by PALTEK. This enables ultra-high speed and reduced power consumption (as compared to CPUs and GPUs), while processing of complicated arithmetic operations along with large amounts of data, typical in deep learning.

Against this background, by combining PALTEK’s long standing experience in design and sales of electronic equipment and technical support from proposal to mass production, along with EdgeCortix’s edge AI acceleration focused technology, we can rapidly bring high performance AI inference capabilities to edge devices. Additionally, this partnership will help provide easily deployable edge AI solutions to companies and system integrators without the need for deep know how on FPGA hardware or software.

Main Initiatives / Collaboration Measures

Establishing this distributor agreement, we will combine the strengths of both companies, accelerate the development and mass production of edge AI solutions that utilize FPGAs, and propose and execute efficient AI applications for meeting the needs of the market. Specifically, solutions that integrate EdgeCortix’s Dynamic Neural Accelerator® IP DNA-F200 & DNA-F100 (FPGA bitstreams) with Alveo ™ U50 FPGA accelerator cards, along with EdgeCortix’s MERA ™ dataflow compiler will be offered.

Naohide Yabuki, President of PALTEK Corporation, had the following to say about this partnership:

“Currently, various AI services are on the market, but most of them are processed on CPUs and GPUs in the cloud. However, there is a need for low latency in fields such as robots, smart cities, and Industry 4.0, which we are targeting. Along with this, edge AI with FPGAs is increasing as many customers demand low power consumption and long-term supply. EdgeCortix focuses on edge AI and provides solutions specialized for lower latency and lower power consumption. We are very much looking forward to achieve synergistic effects by proposing such edge AI focused solutions together with the Xilinx products we handle. ”

Sakyasingha Dasgupta, CEO of Edgecortix, Inc., had the following to say about this partnership:

“We are pleased to establish this partnership with PALTEK Corporation and are confident that it will enable growth in edge AI hardware acceleration business involving FPGAs. We feel very strongly that, with complete integrated solutions leveraging our unique technology, together with PALTEK Corporation, we can enhance the practical application of edge AI products and the overall customer experience. Since 1982, PALTEK Corporation has a wealth of experience in electronic product development and sales, supporting customers from proposal stages to mass production. Leveraging this experience, we will offer our AI processor IP and compiler technology for extremely fast inference on edge devices and datacenters using FPGAs, requiring very little effort for solution deployment.”

About Dynamic Neural Accelerator® IP DNA-F200 from Edge Cortix

DNA-F200 is the latest member of the EdgeCortix Dynamic Neural Accelerator® dataflow architecture based IP family for deep neural network (DNN) inference application on FPGAs. It is designed for the latest Xilinx ALVEO™ U50/U50LV adaptable accelerator cards with HBM support. DNA-F200 (3.7 INT8 TOP/s at 300 MHz) and its predecessor DNA-F100 (2.3 INT8 TOP/s at 275 MHz) are a high-performance convolution neural network (CNN) inference IP optimized for ultra-low latency, energy-efficient and high throughput workloads for streaming data. Especially, designed for blazingly fast edge AI applications. DNA-F200/F100 runs with highly optimized instructions set for INT8 bit batch-size 1 inference and supports all mainstream convolutional neural networks, such as ResNet, YOLO, SSD, MobileNet, FPN, MonoDepth etc. It is supported on any Xilinx or custom board based on Xilinx FPGAs that has a Vitis platform, out of the box. This includes both MPSoC class and datacenter class ALVEO™ FPGAs.

EdgeCortix offers the DNA-F200 bitstream along with their proprietary MERA ™ compiler. This enables nearly zero effort deployment of deep neural networks designed in most popular frameworks like Pytorch and Tensorflow-lite directly on the FPGA. Developed on top of open-source machine learning compiler Apache TVM*3, MERA enables machine learning engineers to optimize and run networks designed for CPUs or GPUs, with INT8 bit quantization out of the box on the DNA IP implemented on Xilinx ALVEO FPGAs. The compiler automatically identifies which parts of the neural network can be offloaded to the accelerator and automatically offloads new or unknown operators to the host processor. The MERA compiler also comes with a built-in simulator and interpreter. After compilation, customers can use these tools for cycle-accurate performance simulation without testing on the hardware as well as to quantify the impact of INT8 bit quantization on network accuracy.

Further details of DNA-F200 and the MERA™ dataflow compiler: https://www.edgecortix.com/

Terms used

1. Alveo ™ U50 Data Center Accelerator Card — An accelerator card from Xilinx that demonstrates excellent performance for high-speed processing such as DNN inference.

For more information, please visit https://www.xilinx.com/products/boards-and-kits/alveo/u50.html

2. Dynamic Neural Accelerator — An AI hardware architecture provided by EdgeCortix focusing on energy-efficient, low latency AI inference on embedded and telco edge devices. DNA-F100/F200 are specifics versions of the IP family targeting FPGAs.

3. Apache TVM is an open source, end-to-end machine learning compiler for CPUs, GPUs and accelerators. https://tvm.apache.org/

4. Vitis is an integrated software framework optimized for Xilinx FPGAs and Versal ACAP hardware platforms. https://www.xilinx.com/products/design-tools/vitis/vitis-platform.html

4. Dynamic Neural Accelerator ® and MERA ™ are registered trademarks or trademarks of EdgeCortix in Japan and other countries.

5. The Xilinx name and other brand names mentioned in this press release are registered trademarks or trademarks of Xilinx in the United States and other countries. All other names belong to their respective owners.

About PALTEK Corporation

Since its founding in 1982, PALTEK has been selling semiconductor products in Japan and overseas to electronics manufacturers, as well as providing contract design services for hardware and software, and as a partner in customer product development, from specification studies to trial production. They support development and mass production. PALTEK will contribute to the development of their customers by providing optimal solutions for them based on their corporate philosophy of “coexistence with diverse entities.”

For more information about PALTEK, please visit https://www.paltek.co.jp/en/index.html

About Edgecortix, Inc.

EdgeCortix, Inc. was founded in 2019 with the corporate mission to “bring cloud-level performance to the embedded edge, for low latency, low cost, and energy-efficient deep neural network inference”. The company’s strength is in its unique artificial intelligence processor technology designed with an integrated hardware and software co-design approach. EdgeCortix has raised a total investment of 525 Million Yen till date from investors in Japan, Singapore and USA. It has a proven track record of achievements with existing partnerships with multiple companies in the electronic manufacturing industry. Taking a software centric approach to AI hardware IP creation, their Dynamic Neural Accelerator™ IP core and MERA™ compiler is designed to work with little effort across custom ASICs and FPGAs.

For more information about Edgecortix, please visit https://www.edgecortix.com

For inquiries regarding this matter

Edgecortix, Inc

Public Relations Officer

pr@edgecortix.com

Inquiries about products and services

Edgecortix, Inc

AI Hardware Accelerator Team

info@edgecortix.com